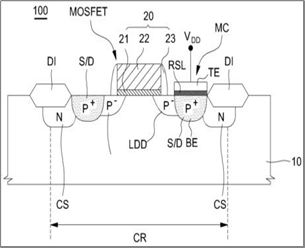

- 요약 본 발명의 실시예들은 반도체 메모리 소자에 관한 것으로서, 더욱 상세하게는, 비휘발성 메모리 소자인 가변 저항 메모리 소자 및 이의 제조 방법에 관한 것이다. 본 발명의 일 실시예에 따른 가변 저항 메모리 소자는 실리콘 전극층, 상기 실리콘 전극층 상의 게르마늄 산화물 박막을 포함하는 가변 저항층 및 상기 실리콘 전극층에 대향하는 금속 전극층을 포함할 수 있고, 상기 실리콘 전극층은 기판의 활성 표면에 형성된 P형 전계 효과 트랜지스터의 소오스/드레인 영역을 포함할 수 있으며, 상기 게르마늄 산화물 박막은 상기 소오스/드레인 영역에 직접 접촉되어 상기 P형 전계 효과 트랜지스터와 비휘발성 메모리 셀이 직렬 연결될 수 있고, 상기 비휘발성 메모리 셀은 상기 가변 저항층을 포함하여 구성될 수 있고, 상기 소오스/드레인 영역은 상기 P형 전계 효과 트랜지스터의 소오스/드레인이면서 상기 비휘발성 메모리 셀의 하부 전극으로서 기능을 동시에 수행할 수 있다.

- 대표 청구항 실리콘 전극층; 상기 실리콘 전극층 상의 게르마늄 산화물 박막을 포함하는 가변 저항층; 및 상기 실리콘 전극층에 대향하는 금속 전극층을 포함하고, 상기 실리콘 전극층은 기판의 활성 표면에 형성된 P형 전계 효과 트랜지스터의 소오스/드레인 영역을 포함하며, 상기 게르마늄 산화물 박막은 상기 소오스/드레인 영역에 직접 접촉되어 상기 P형 전계 효과 트랜지스터와 비휘발성 메모리 셀이 직렬 연결되고, 상기 비휘발성 메모리 셀은 상기 가변 저항층을 포함하여 구성되고, 상기 소오스/드레인 영역은 상기 P형 전계 효과 트랜지스터의 소오스/드레인이면서 상기 비휘발성 메모리 셀의 하부 전극으로서 기능을 동시에 수행하는 가변 저항 메모리 소자.

-

대표 도면

-

전략기술 분류

반도체·디스플레이

고집적, 저항기반 메모리 - 출원번호 10-2024-0041199 KIPRIS

- 출원일 2024-03-26

- 공개번호 10-2024-0045190

- 공개일 2024-04-05

- 등록번호

- 등록일

- 우선권 번호

- 우선권 국가

- 우선권 주장일

- 현재 상태 심사중

- 현재 권리자

- IPC 코드 H10N-070/00

Copyright ⓒ 한국연구재단 기술사업화센터 (NRF-TCC) All rights reserved.