- 요약 본 개시의 몇몇 실시예에 따른 프로세서를 포함하는 컴퓨팅 장치에서 양자 키 교환 시에 전력 부채널 공격을 방지하기 위한 방법으로서, 양자 회로를 이용하여, 0 또는 1을 포함하는 비트를 10 또는 01을 포함하는 변환 비트로 인코딩하는 단계; 상기 변환 비트를 이용한 외부 기기와의 양자 키 교환(Quantum Key Distribution)을 통해 적어도 하나의 변환 비트를 포함하는 제 1 키(key)를 획득하는 단계; 및 10 또는 01을 출력하는 XOR 연산 회로를 이용하여, 상기 적어도 하나의 변환 비트 각각에 대한 적어도 하나의 제 1 연산 결과 비트를 획득하는 단계;를 포함할 수 있다.

- 대표 청구항 프로세서를 포함하는 컴퓨팅 장치에서 양자 키 교환 시에 전력 부채널 공격을 방지하기 위한 방법으로서,양자 회로를 이용하여, 0 또는 1을 포함하는 비트를 10 또는 01을 포함하는 변환 비트로 인코딩하는 단계;상기 변환 비트를 이용한 외부 기기와의 양자 키 교환(Quantum Key Distribution)을 통해 적어도 하나의 변환 비트를 포함하는 제 1 키(key)를 획득하는 단계; 및10 또는 01을 출력하는 XOR 연산 회로를 이용하여, 상기 적어도 하나의 변환 비트 각각에 대한 적어도 하나의 제 1 연산 결과 비트를 획득하는 단계;를 포함하는,방법.

-

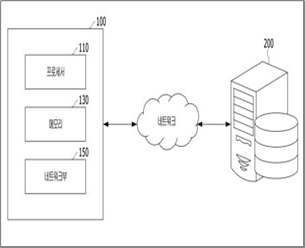

대표 도면

-

전략기술 분류

양자

양자컴퓨팅 - 출원번호 10-2022-0175420 KIPRIS

- 출원일 2022-12-15

- 공개번호 10-2023-0095822

- 공개일 2023-06-29

- 등록번호

- 등록일

- 우선권 번호 10-2021-0184590

- 우선권 국가 KR

- 우선권 주장일 2021-12-22

- 현재 상태 심사중

- 현재 권리자

- IPC 코드 H04L-009/40, H04L-009/08

Copyright ⓒ 한국연구재단 기술사업화센터 (NRF-TCC) All rights reserved.