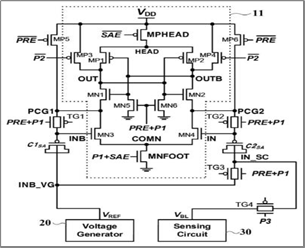

- 요약 본 개시는 입력 노드쌍으로 인가되는 차동의 입력 전압을 감지 및 증폭하여 출력 노드쌍으로 차동 출력 전압을 출력하는 센스 앰프 회로 및 기준 전압이 인가되면 기준 전압 노드 및 센싱 노드로 공급하여 바이어싱하고, 이후 인가되는 입력 전압을 센싱 노드로 전달하여, 기준 전압과 입력 전압 사이의 전압차를 나타내는 입력 전압차를 커플링을 통해 입력 노드쌍 중 하나로 인가하는 오프셋 제거 회로를 포함하여 오프셋을 제거하여 센싱 수율을 향상시킬 수 있을 뿐만 아니라, 차동 입력단에 기준 전압을 바이어싱함으로써 넓은 입력 전압 범위에서 안정적으로 동작할 수 있는 전류 래치 센스 앰프 및 메모리 장치를 제공한다.

- 대표 청구항 기준 전압과 입력 전압 사이의 전압차를 감지 및 증폭하여 출력하는 전류 래치 센스 앰프에 있어서, 입력 노드쌍으로 인가되는 차동의 입력 전압을 감지 및 증폭하여 출력 노드쌍으로 차동 출력 전압을 출력하는 센스 앰프 회로; 및 상기 기준 전압이 인가되면 기준 전압 노드 및 센싱 노드로 공급하여 바이어싱하고, 이후 인가되는 상기 입력 전압을 상기 센싱 노드로 전달하여, 상기 기준 전압과 상기 입력 전압 사이의 전압차를 나타내는 입력 전압차를 커플링을 통해 상기 입력 노드쌍 중 하나로 인가하는 오프셋 제거 회로를 포함하되, 상기 오프셋 제거 회로는 프리차지 구간과 오프셋 캡쳐 구간, 신호 입력 구간 및 센싱 구간으로 구분되는 상기 전류 래치 센스 앰프의 동작 구간 중 상기 오프셋 캡쳐 구간에 상기 입력 노드쌍이 상기 센스 앰프 회로의 오프셋을 유발하는 트랜지스터의 문턱값에 따른 전압 레벨을 갖도록 하여 오프셋을 제거하고, 상기 오프셋 제거 회로는 상기 신호 입력 구간에 상기 문턱값에 따른 전압 레벨을 갖는 상기 입력 노드쌍 중 하나로 상기 입력 전압차와 상기 문턱값에 따른 전압의 합에 따른 전압을 인가하는 전류 래치 센스 앰프.

-

대표 도면

-

전략기술 분류

반도체·디스플레이

고집적, 저항기반 메모리 - 출원번호 10-2023-0119673 KIPRIS

- 출원일 2023-09-08

- 공개번호

- 공개일

- 등록번호 10-2652188

- 등록일 2024-03-25

- 우선권 번호

- 우선권 국가

- 우선권 주장일

- 현재 상태 등록

- 현재 권리자 연세대학교 산학협력단

- IPC 코드 G11C-007/06

Copyright ⓒ 한국연구재단 기술사업화센터 (NRF-TCC) All rights reserved.