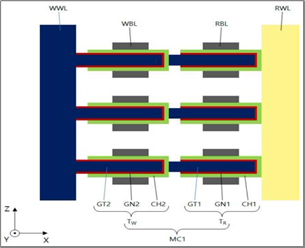

- 요약 커패시터리스 3차원 적층형 DRAM 소자 및 그 제조 방법에 관해 개시되어 있다. 개시된 커패시터리스 3차원 적층형 DRAM 소자는 수평 방향 및 수직 방향으로 상호 이격하여 배열된 것으로, 각각이 제 1 채널층, 제 1 게이트 절연층 및 제 1 게이트 전극을 포함하는 수평형 읽기 트랜지스터 구조 및 상기 제 1 게이트 전극에 전기적으로 연결된 제 2 채널층, 제 2 게이트 절연층 및 제 2 게이트 전극을 포함하는 수평형 쓰기 트랜지스터 구조를 포함하는 복수의 메모리셀 구조, 상기 복수의 메모리셀 구조의 복수의 상기 쓰기 트랜지스터 구조에 연결된 것으로, 수평 방향으로 연장된 복수의 쓰기 비트 라인, 상기 복수의 메모리셀 구조의 복수의 상기 읽기 트랜지스터 구조에 연결된 것으로, 수평 방향으로 연장된 복수의 읽기 비트 라인, 상기 복수의 쓰기 트랜지스터 구조에 연결된 것으로, 수직 방향으로 연장된 복수의 쓰기 워드 라인 및 상기 복수의 읽기 트랜지스터 구조에 연결된 것으로, 수직 방향으로 연장된 복수의 읽기 워드 라인을 포함할 수 있다.

- 대표 청구항 기판 상에 서로 다른 물질로 구성된 제 1 및 제 2 물질층이 교대로 반복 적층된 구조를 갖는 적층체를 형성하는 단계; 상기 적층체를 패터닝하여 상기 제 1 물질층으로부터 얻어진 제 1 물질층 패턴 및 상기 제 2 물질층으로부터 얻어진 제 2 물질층 패턴을 구비한 복수의 패턴부를 갖는 패턴화된 적층체를 형성하되, 상기 복수의 패턴부는 제 1 방향으로 연장되고 상기 제 1 방향에 직교하는 제 2 방향으로 상호 이격된 상기 패턴화된 적층체를 형성하는 단계; 상기 복수의 패턴부 사이에 매립 물질을 충진하여 상기 패턴화된 적층체와 상기 매립 물질을 포함하는 구조체를 형성하는 단계; 상기 구조체에 상기 복수의 패턴부 각각을 수직 방향으로 관통하는 것으로, 상기 제 1 방향으로 상호 이격된 제 1 및 제 2 수직홀을 형성하는 단계; 상기 구조체의 상기 제 1 및 제 2 수직홀 각각의 주위에서 상기 제 1 물질층 패턴과 상기 매립 물질을 리세스하여 상기 제 2 물질층 패턴을 노출시키는 제 1 및 제 2 리세스부를 형성하는 단계; 상기 구조체로부터, 상기 제 1 리세스부에서 상기 제 2 물질층 패턴을 둘러싸면서 수평 방향으로 연장된 쓰기 비트 라인(write bit line), 상기 제 2 리세스부에서 상기 제 2 물질층 패턴을 둘러싸면서 수평 방향으로 연장된 읽기 비트 라인(read bit line), 및 상기 쓰기 비트 라인과 상기 읽기 비트 라인 주위의 공간을 메우는 충진 절연층을 포함하는 중간소자 구조체를 형성하는 단계; 상기 중간소자 구조체에서 상기 제 1 수직홀에 대응하는 영역에 제 3 수직홀을 형성하는 단계; 상기 제 3 수직홀에 의해 노출된 상기 제 2 물질층 패턴을 제거하여 상기 제 1 방향으로 연장되고 상기 쓰기 비트 라인과 상기 읽기 비트 라인을 노출시키는 수평홀을 형성하는 단계; 상기 수평홀 내에 상기 읽기 비트 라인에 전기적으로 접속된 것으로, 제 1 채널층, 제 1 게이트 절연층 및 제 1 게이트 전극을 포함하는 읽기 트랜지스터(read transistor) 구조를 형성하는 단계; 상기 수평홀 내에서 상기 쓰기 비트 라인에 전기적으로 접속된 것으로, 제 2 채널층, 제 2 게이트 절연층 및 제 2 게이트 전극을 포함하는 쓰기 트랜지스터(write transistor) 구조를 형성하되, 상기 제 2 채널층이 상기 제 1 게이트 전극에 전기적으로 연결되도록 상기 쓰기 트랜지스터 구조를 형성하는 단계; 및 상기 제 1 수직홀에 대응하는 영역에 상기 제 2 게이트 전극과 전기적으로 연결되고 수직 방향으로 연장된 쓰기 워드 라인(write word line)을 형성하고, 상기 제 2 수직홀에 대응하는 영역에 상기 제 1 채널층과 전기적으로 연결되고 수직 방향으로 연장된 읽기 워드 라인(read word line)을 형성하는 단계를 포함하는 커패시터리스 3차원 적층형 DRAM 소자의 제조 방법.

-

대표 도면

-

전략기술 분류

반도체·디스플레이

고집적, 저항기반 메모리 - 출원번호 10-2023-0067638 KIPRIS

- 출원일 2023-05-25

- 공개번호

- 공개일

- 등록번호 10-2649968

- 등록일 2024-03-18

- 우선권 번호

- 우선권 국가

- 우선권 주장일

- 현재 상태 등록

- 현재 권리자 서울대학교산학협력단

- IPC 코드 H10B-012/00, H01L-029/786, G11C-011/4097

Copyright ⓒ 한국연구재단 기술사업화센터 (NRF-TCC) All rights reserved.