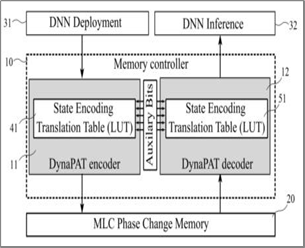

- 요약 개시된 실시예는 다수의 저항 상태 레벨 중 저항값이 포함된 저항 상태 레벨에 따라 각각 멀티 비트의 데이터를 저장하는 상변이 메모리(Multi-Level Cell-Phase Change Memory: 이하 PCM)로 구현된 다수의 메모리 셀을 구비하는 셀 어레이 및 DNN(Deep Neural Network: 이하 DNN)을 구성하는 다수의 레이어에 포함되는 다수의 가중치의 비트 패턴에 대한 출현 비율에 따라, 각 비트 패턴과 저항 상태 레벨을 맵핑하여 멀티 비트의 데이터를 메모리 셀에 저장하는 메모리 컨트롤러를 포함하여 저항 드리프트 현상에 의한 데이터 오류가 발생되는 빈도를 저감시켜 내결함성을 향상시킬 수 있는 DNN을 위한 PCM 기반 메모리 장치 및 이의 가중치 저장 방법을 제공한다.

- 대표 청구항 다수의 저항 상태 레벨 중 저항값이 포함된 저항 상태 레벨에 따라 각각 멀티 비트의 데이터를 저장하는 상변이 메모리(Multi-Level Cell-Phase Change Memory: 이하 PCM)로 구현된 다수의 메모리 셀을 구비하는 셀 어레이; 및 DNN(Deep Neural Network: 이하 DNN)을 구성하는 다수의 레이어에 포함되는 다수의 가중치의 비트 패턴에 대한 출현 비율에 따라, 각 비트 패턴과 상기 저항 상태 레벨을 맵핑하여 멀티 비트의 데이터를 상기 메모리 셀에 저장하는 메모리 컨트롤러를 포함하는 DNN을 위한 PCM 기반 메모리 장치.

-

대표 도면

-

전략기술 분류

반도체·디스플레이

고집적, 저항기반 메모리 - 출원번호 10-2022-0151360 KIPRIS

- 출원일 2022-11-14

- 공개번호 10-2024-0070035

- 공개일 2024-05-21

- 등록번호

- 등록일

- 우선권 번호

- 우선권 국가

- 우선권 주장일

- 현재 상태 심사중

- 현재 권리자

- IPC 코드 G06N-003/063, G06N-003/04, G11C-013/00

Copyright ⓒ 한국연구재단 기술사업화센터 (NRF-TCC) All rights reserved.