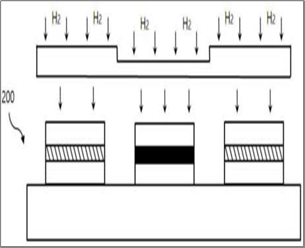

- 요약 본 발명은 반도체 소자의 제조 방법에 관한 것이다. 일 실시예에 따른 반도체 소자의 제조 방법은, 기판 상에 배치되는 복수의 서브 반도체 소자를 포함하는 반도체 소자를 준비하는 단계, 상기 반도체 소자의 상부에 선택적 투과 마스크를 배치하는 단계 및 수소 가스 분위기에서 상기 반도체 소자에 대한 열처리를 수행하는 단계를 포함할 수 있다. 일 실시예에서, 상기 선택적 투과 마스크는 서로 다른 수소 투과율을 갖는 복수의 투과 제어 영역을 포함할 수 있다. 일 실시예에서, 각각의 투과 제어 영역은 각각의 서브 반도체 소자의 위치와 대응될 수 있다.

- 대표 청구항 기판 상에 배치되는 복수의 서브 반도체 소자를 포함하는 반도체 소자를 준비하는 단계;상기 반도체 소자의 상부에 선택적 투과 마스크를 배치하는 단계; 및수소 가스 분위기에서 상기 반도체 소자에 대한 열처리를 수행하는 단계를 포함하고,상기 선택적 투과 마스크는 서로 다른 수소 투과율을 갖는 복수의 투과 제어 영역을 포함하고,각각의 투과 제어 영역은 각각의 서브 반도체 소자의 위치와 대응되는반도체 소자의 제조 방법.

-

대표 도면

-

전략기술 분류

반도체·디스플레이

고성능, 저전력 인공지능 반도체 - 출원번호 10-2023-0091721 KIPRIS

- 출원일 2023-07-14

- 공개번호 10-2024-0011098

- 공개일 2024-01-25

- 등록번호

- 등록일

- 우선권 번호 10-2022-0087899, 10-2022-0087906

- 우선권 국가 KR, KR

- 우선권 주장일

- 현재 상태 심사중

- 현재 권리자

- IPC 코드 H01L-021/324, H01L-021/67

Copyright ⓒ 한국연구재단 기술사업화센터 (NRF-TCC) All rights reserved.