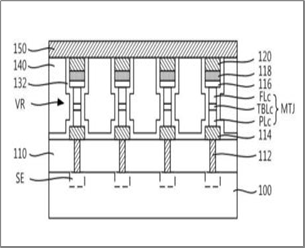

- 요약 본 발명은 가변 저항 메모리 소자 및 그 제조 방법에 관한 것으로, 제1 도전 라인들, 상기 제1 도전 라인들과 교차하는 제2 도전 라인들 및 상기 제1 도전 라인들과 제2 도전 라인들 사이의 교차점들에 각각 제공되는 메모리 셀들을 포함하고, 메모리 셀들의 각각은 선택 소자 및 가변 저항 구조체를 포함하되, 상기 가변 저항 구조체는 차례로 적층된 하부 전극, 자기터널접합, 캡핑 패턴, 스트레스 인가 패턴 및 상부 전극을 포함하고. 상기 자기터널접합은 고정층 패턴, 자유층 패턴 및 이들 사이에 개재된 터널 배리어층 패턴을 포함하고, 상기 스트레스 인가 패턴은 인장 스트레스(tensile stress)를 갖는 도전 물질을 포함하고, 상기 고정층 패턴, 상기 자유층 패턴 및 상기 터널 배리어층 패턴의 폭은 상기 캡핑 패턴 및 상기 스트레스 인가패턴의 폭보다 작은 가변 저항 메모리 소자를 제공한다.

- 대표 청구항 제1 도전 라인들; 상기 제1 도전 라인들과 교차하는 제2 도전 라인들; 및 상기 제1 도전 라인들과 제2 도전 라인들 사이의 교차점들에 각각 제공되는 메모리 셀들을 포함하고, 메모리 셀들의 각각은 선택 소자 및 가변 저항 구조체를 포함하되, 상기 가변 저항 구조체는 차례로 적층된 하부 전극, 자기터널접합, 캡핑 패턴, 스트레스 인가 패턴 및 상부 전극을 포함하고, 상기 자기터널접합은 고정층 패턴, 자유층 패턴 및 이들 사이에 개재된 터널 배리어층 패턴을 포함하고, 상기 스트레스 인가 패턴은 인장 스트레스(tensile stress)를 갖는 도전 물질을 포함하고, 상기 고정층 패턴, 상기 자유층 패턴 및 상기 터널 배리어층 패턴의 폭은 상기 캡핑 패턴 및 상기 스트레스 인가패턴의 폭보다 작고, 상기 캡핑 패턴 및 상기 스트레스 인가 패턴의 일 측면들은 공면을 이루고, 상기 캡핑 패턴 및 상기 스트레스 인가 패턴의 상기 일 측면들에 인접한 상기 자기터널접합의 일 측면은 상기 일 측면들과 정렬되지 않고 내측으로 만입된 형태를 갖는 가변 저항 메모리 소자.

-

대표 도면

-

전략기술 분류

반도체·디스플레이

고집적, 저항기반 메모리 - 출원번호 10-2023-0007944 KIPRIS

- 출원일 2023-01-19

- 공개번호

- 공개일

- 등록번호 10-2665796

- 등록일 2024-05-08

- 우선권 번호

- 우선권 국가

- 우선권 주장일

- 현재 상태 등록

- 현재 권리자 삼육대학교산학협력단

- IPC 코드 H10B-061/00, H10N-050/10, H10N-050/80, H10N-059/00

Copyright ⓒ 한국연구재단 기술사업화센터 (NRF-TCC) All rights reserved.